Lynn Choi Yunheung Paek Sangyeun Cho (Eds.)

# Advances in Computer Systems Architecture

12th Asia-Pacific Conference, ACSAC 2007 Seoul, Korea, August 2007 Proceedings

#### Lecture Notes in Computer Science 4697

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

David Hutchison

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Moshe Y. Vardi

Rice University, Houston, TX, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

Lynn Choi Yunheung Paek Sangyeun Cho (Eds.)

## Advances in Computer Systems Architecture

12th Asia-Pacific Conference, ACSAC 2007 Seoul, Korea, August 23-25, 2007 Proceedings

#### Volume Editors

Lynn Choi Korea University School of Electrical Engineering Anam-Dong, Sungbuk-Ku, Seoul, Korea E-mail: lchoi@korea.ac.kr

Yunheung Paek Seoul National University School of Electrical Engineering Seoul, Korea E-mail: ypaek@snu.ac.kr

Sangyeun Cho University of Pittsburgh Department of Computer Science Pittsburgh, PA 15260, USA E-mail: cho@cs.pitt.edu

Library of Congress Control Number: 2007932678

CR Subject Classification (1998): B.2, B.4, B.5, C.2, C.1, D.4

LNCS Sublibrary: SL 1 – Theoretical Computer Science and General Issues

ISSN 0302-9743

ISBN-10 3-540-74308-1 Springer Berlin Heidelberg New York ISBN-13 978-3-540-74308-8 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springer.com

© Springer-Verlag Berlin Heidelberg 2007 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 12109494 06/3180 5 4 3 2 1 0

#### **Preface**

On behalf of the program and organizing committee members of this conference, we are pleased to present you with the proceedings of the 12<sup>th</sup> Asia-Pacific Computer Systems Architecture Conference (ACSAC 2007), which was hosted in Seoul, Korea on August 23-25, 2007. This conference has traditionally been a forum for leading researchers in the Asian, American and Oceanian regions to share recent progress and the latest results in both architectural and system issues. In the past few years the conference has become more international in the sense that the geographic origin of participants has become broader to include researchers from all around the world, including Europe and the Middle East.

This year, we received 92 paper submissions. Each submission was reviewed by at least three primary reviewers along with up to three secondary reviewers. The total number of completed reviews reached 333, giving each submission 3.6 reviews on average. All the reviews were carefully examined during the paper selection process, and finally 26 papers were accepted, resulting in an acceptance rate of about 28%. The selected papers encompass a wide range of topics, with much emphasis on hardware and software techniques for state-of-the-art multicore and multithreaded architectures. In addition to the regular papers, the technical program of the conference included eight invited papers from world-class renowned researchers and featured two keynotes by Pen-Chung Yew (University of Minnesota) and Kunio Uchiyama (Hitachi), addressing a compiler framework for speculative multithreading and power-efficient heterogeneous multicore chip development, respectively. We sincerely hope that the proceedings will serve as a valuable reference for researchers and developers alike.

Putting together ACSAC 2007 was a team effort. First of all, we would like to express our special gratitude to the authors and speakers for providing the contents of the program. We would also like to thank the program committee members and external reviewers for diligently reviewing the papers and providing suggestions for their improvements. We believe that you will find the outcome of their efforts in this book. In addition, we extend our thanks to the organizing committee members and student volunteers, who contributed enormously to various aspects of conference administration. Finally, we would like to express special thanks to Chris Jesshope and Jinling Xue for sharing their experience and offering fruitful feedback in the early stages of preparing the conference.

June 2007

Lynn Choi Yunheung Paek Sangyeun Cho

#### **Conference Organization**

#### **General Co-chairs**

Lynn Choi Korea University, Korea

Sung Bae Park Samsung Electronics, Korea

#### **Program Co-chairs**

Yunheung Paek

John Morris

University of Auckland, New Zealand

Sangyeun Cho

University of Pittsburgh, USA

#### **Publicity Chair**

Ki-Seok Chung Hanyang University, Korea

#### **Publication Chair**

Hwangnam Kim Korea University, Korea

#### **Local Arrangement Chair**

Sung Woo Chung Korea University, Korea

#### **Finance Chair**

Yunmook Nah Dankook University, Korea

#### **Registration Chair**

Youngho Choi Konkuk University, Korea

#### **Steering Committee**

Jesse Z. Fang Intel, USA

James R. Goodman University of Auckland, New Zealand

Gernot Heiser National ICT, Australia

#### VIII Organization

Kei Hiraki Tokyo University, Japan

Chris Jesshope University of Amsterdam, Netherlands Feipei Lai National Taiwan University, Taiwan John Morris University of Auckland, New Zealand

Amos Omondi Yonsei University, Korea Ronald Pose Monash University, Australia Stanislav Sedukhin University of Aizu, Japan

Mateo Valero Universitat Politecnica de Catalunya, Spain Jingling Xue University of New South Wales, Australia

Pen-Chung Yew University of Minnesota, USA

#### **Program Committee**

Jin Young Choi Korea University, Korea

Bruce Christianson University of Hertfordshire, U

Bruce Christianson University of Hertfordshire, UK Sung Woo Chung Korea University, Korea

Oliver Diessel University of New South Wales, Australia

Colin Egan University of Hertfordshire, UK Skevos Evripidou University of Cyprus, Cyprus

Wong Weng Fai National University of Singapore, Singapore

Michael Freeman University of York, UK Guang G. Gao University of Delaware, USA

Jean-Luc Gaudiot University of California at Irvine, USA

Alex Gontmakher Technion, Israel

Gernot Heiser National ICT, Australia

Wei-Chung Hsu University of Minnesota, USA

Suntae Hwang Kookmin University, Korea

Chris Jesshope University of Amsterdam, Netherlands

Jeremy Jones Trinity College, Ireland

Norman P. Jouppi Hewlett Packard, USA

Cheol Hong Kim Chonnam University, Korea

Doohyun Kim Kunkook University, Korea

Feipei Lai National Taiwan University, Taiwan

Hock Beng Lim Nanyang Technological University, Singapore

Philip Machanick University of Queensland, Australia Worawan Marurngsith Thammasat University, Thailand

Henk Muller University of Bristol, UK

Sukumar Nandi Indian Institute of Technology Guwahati, India

Tin-Fook Ngai Intel China Research Center, China

Amos Omondi Yonsei University, Korea

L M Patnaik Indian Institute of Science Bangalore, India Andy Pimentel University of Amsterdam, Netherlands

Ronald Pose Monash University, Australia Stanislav G. Sedukhin University of Aizu, Japan

Won Shim Seoul National University of Technology, Korea

Mark Smotherman Clemson University, USA

K. Sridharan Indian Institute of Technology Madras, India

Rajeev Thakur Argonne National Laboratory, USA

Mateo Valero Universitat Politecnica de Catalunya, Spain

Lucian N. Vintan University of Sibiu, Romania

Chengyong Wu ICT, Chinese Academy of Sciences, China Zhi-Wei Xu ICT, Chinese Academy of Sciences, China Jingling Xue University of New South Wales, Australia

Pen-Chung Yew University of Minnesota, USA

#### **External Reviewers**

Nidhi Aggarwal Kai Hwang Naveen Muralimanohar

Nadeem Ahmed Lei Jin Sudha Natarajan

Christopher Ang Jonghee Kang Venkatesan Packirisamy

Elizabeth M. Belding-Royer Kamil Kedzierski Chanik Park Darius Buntinas Daeho Kim Jagdish Patra

Francisco Cazorla Jinpyo Kim Vladimir Pervouchine

José M. Cela

John Kim

Vinod Prasad

Yang Chen

Chung-Ta King

Ken Robinson

Doosan Cho

Tei-Wei Kuo

Esther Salamí

Peter Chubb

Ihor Kuz

Oliverio J. Santana

Ian Clough

Koen Langendoen

Michael Schelansker

Toni Cortés Robert Latham Bill Scherer Kyriacou Costas Sanghwan Lee Bertil Schmidt Adrián Cristal Heung-No Lee Ahmed Sherif Abhinay Das Hyunjin Lee Todor P. Stefanov Amitabha Das Graham Leedham Mark Thompson Michel Dubois Binghao Li Jordi Torres Bin Fan Huiyun Li Nian-Feng Tzeng Jinyun Fang Kuan-Ching Li Lei Wang

Yu-Chiann Foo Wei Li Yulu Yang

John Glossner Adam Postula Jia Yu

Sandeep K. Gupta Chen Liu Patryk Zadarnowski Rubén Conzález Shaoshan Liu Ahmed Zekri

Rogeli GrimaJie MaGe ZhangJizhong HanLuke MacphersonJony ZhangPaul HavingaPramod K. MeherLongbing ZhangMichael HicksNeill MillerYoutao Zhang

Houman Homayoun Miquel Moreto

#### **Student Volunteers**

Yong-Soo Bae Hyun-Joon Lee Keunhee Yeo Jae Kyun Jung Kiyeon Lee Jonghee Youn

Daeho Kim Sang-Hoon Lee

#### **Table of Contents**

| A Compiler Framework for Supporting Speculative Multicore Processors (Keynote)                                | 1  |

|---------------------------------------------------------------------------------------------------------------|----|

| Power-Efficient Heterogeneous Multicore Technology for Digital<br>Convergence (Keynote)                       | 2  |

| StarDBT: An Efficient Multi-platform Dynamic Binary Translation System                                        | 4  |

| Unbiased Branches: An Open Problem                                                                            | 16 |

| An Online Profile Guided Optimization Approach for Speculative Parallel Threading                             | 28 |

| Entropy-Based Profile Characterization and Classification for Automatic Profile Management                    | 40 |

| Laplace Transformation on the FT64 Stream Processor                                                           | 52 |

| Towards Data Tiling for Whole Programs in Scratchpad Memory Allocation                                        | 63 |

| Evolution of NAND Flash Memory Interface                                                                      | 75 |

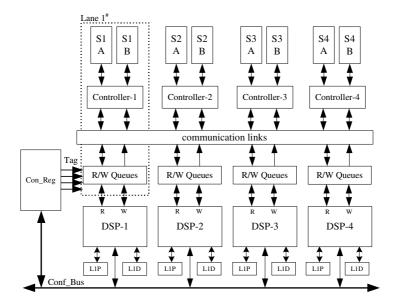

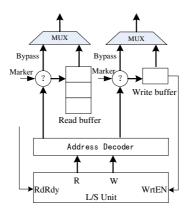

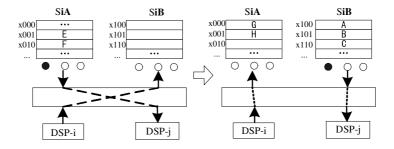

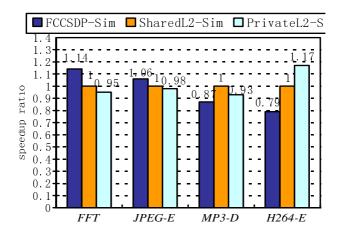

| FCC-SDP: A Fast Close-Coupled Shared Data Pool for Multi-core DSPs                                            | 80 |

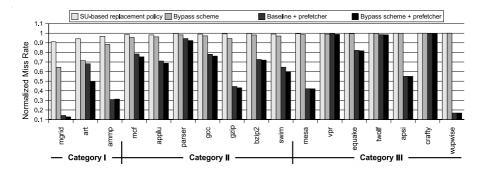

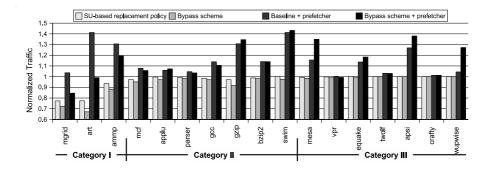

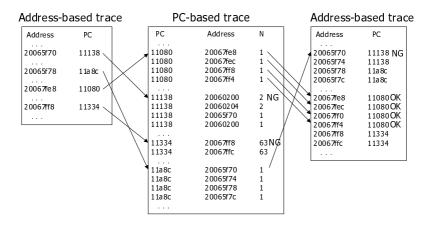

| Exploiting Single-Usage for Effective Memory Management  Thomas Piquet, Olivier Rochecouste, and André Seznec | 90 |

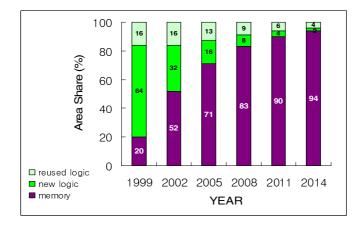

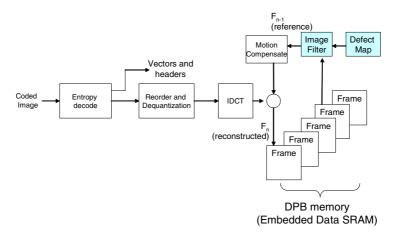

| An Alternative Organization of Defect Map for Defect-Resilient Embedded On-Chip Memories                                           | 1 |

|------------------------------------------------------------------------------------------------------------------------------------|---|

| Kang Yi, Shih-Yang Cheng, Young-Hwan Park, Fadi Kurdahi, and Ahmed Eltawil                                                         | 1 |

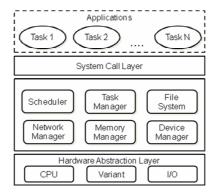

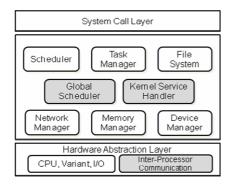

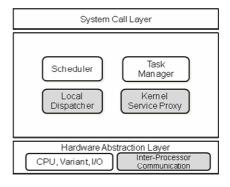

| An Effective Design of Master-Slave Operating System Architecture for Multiprocessor Embedded Systems                              | 1 |

| Minsoo Ryu                                                                                                                         |   |

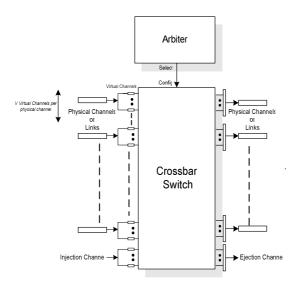

| Optimal Placement of Frequently Accessed IPs in Mesh NoCs                                                                          | 1 |

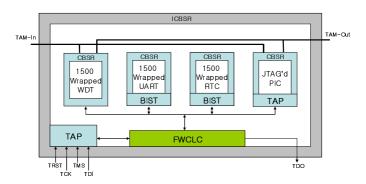

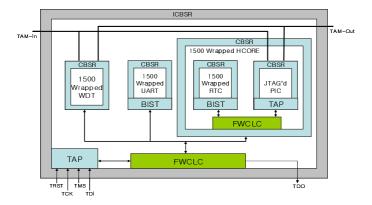

| An Efficient Link Controller for Test Access to IP Core-Based                                                                      | 1 |

| Embedded System Chips  Jaehoon Song, Hyunbean Yi, Juhee Han, and Sungju Park                                                       | 1 |

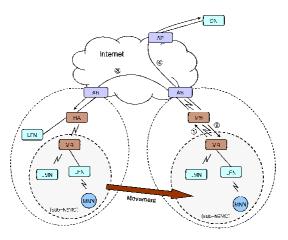

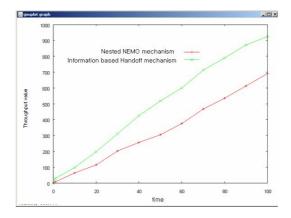

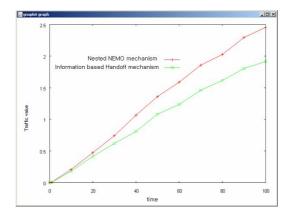

| Performance of Keyword Connection Algorithm in Nested Mobility Networks                                                            | 1 |

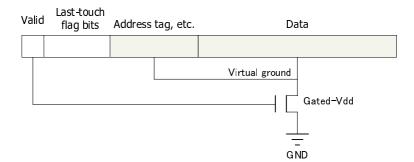

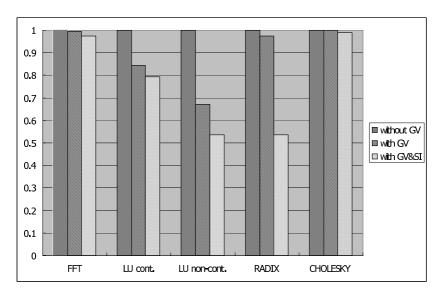

| Leakage Energy Reduction in Cache Memory by Software Self-invalidation                                                             | 1 |

| Exploiting Task Temperature Profiling in Temperature-Aware Task Scheduling for Computational Clusters                              | 1 |

| Runtime Performance Projection Model for Dynamic Power  Management                                                                 | 1 |

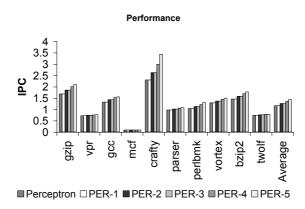

| A Power-Aware Alternative for the Perceptron Branch Predictor                                                                      | 1 |

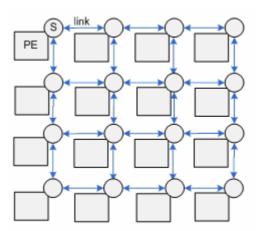

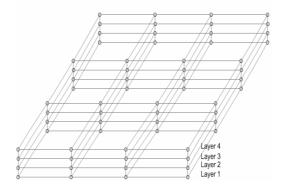

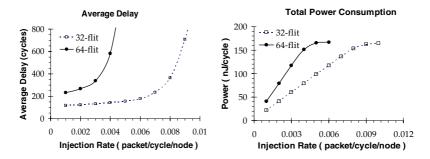

| Power Consumption and Performance Analysis of 3D NoCs                                                                              | 2 |

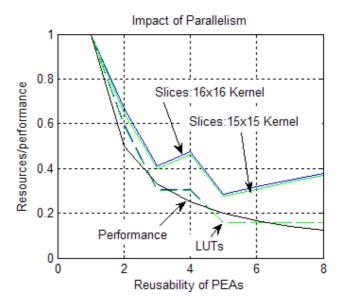

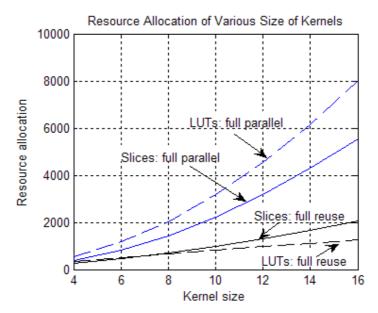

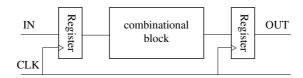

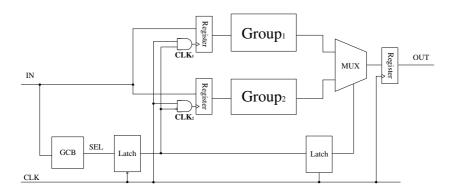

| A Design Methodology for Performance-Resource Optimization of a<br>Generalized 2D Convolution Architecture with Quadrant Symmetric |   |

| Kernels                                                                                                                            | 2 |

| Bipartition Architecture for Low Power JPEG Huffman Decoder                                                                        | 2 |

| A SWP Specification for Sequential Image Processing Algorithms                                                                     | 2 |

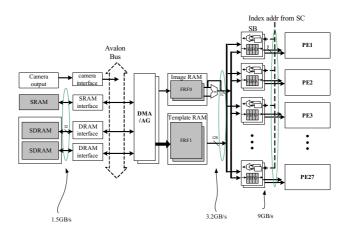

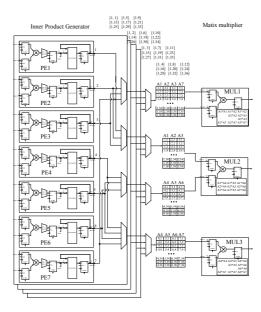

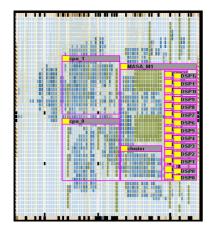

| A Stream System-on-Chip Architecture for High Speed Target<br>Recognition Based on Biologic Vision                                                                                                  | 256  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Nan Wu, Qianming Yang, Mei Wen, Yi He, Changqing Xun, and Chunyuan Zhang                                                                                                                            | 200  |

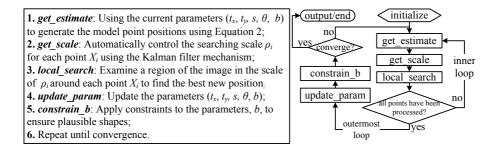

| FPGA-Accelerated Active Shape Model for Real-Time People                                                                                                                                            | 200  |

| Tracking                                                                                                                                                                                            | 268  |

| Performance Evaluation of Evolutionary Multi-core and Aggressively                                                                                                                                  |      |

| Multi-threaded Processor Architectures                                                                                                                                                              | 280  |

| Synchronization Mechanisms on Modern Multi-core Architectures Shaoshan Liu and Jean-Luc Gaudiot                                                                                                     | 290  |

| Concerning with On-Chip Network Features to Improve Cache                                                                                                                                           | 20.4 |

| Coherence Protocols for CMPs                                                                                                                                                                        | 304  |

| Generalized Wormhole Switching: A New Fault-Tolerant Mathematical Model for Adaptively Wormhole-Routed Interconnect Networks F. Safaei, A. Khonsari, M. Fathy, N. Talebanfard, and M. Ould-Khaoua   | 315  |

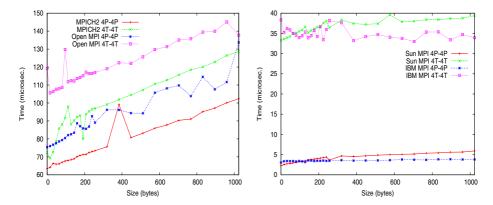

| Open Issues in MPI Implementation                                                                                                                                                                   | 327  |

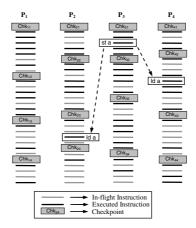

| Implicit Transactional Memory in Kilo-Instruction Multiprocessors Marco Galluzzi, Enrique Vallejo, Adrián Cristal, Fernando Vallejo, Ramón Beivide, Per Stenström, James E. Smith, and Mateo Valero | 339  |

| Design of a Low-Power Embedded Processor Architecture Using Asynchronous Function Units                                                                                                             | 354  |

| A Bypass Mechanism to Enhance Branch Predictor for SMT                                                                                                                                              |      |

| Processors                                                                                                                                                                                          | 364  |

| Thread Priority-Aware Random Replacement in TLBs for a                                                                                                                                              | 970  |

| High-Performance Real-Time SMT Processor                                                                                                                                                            | 376  |

| Architectural Solution to Object-Oriented Programming                                                                                                                                               | 387  |

| Author Index                                                                                                                                                                                        | 399  |

#### A Compiler Framework for Supporting Speculative Multicore Processors

Pen-Chung Yew

University of Minnesota at Twin Cities

As multi-core technology is currently being deployed in computer industry primarily to limit power consumption and improve throughput, continued performance improvement of a *single application* on such systems remains an important and challenging task. Because of the shortened on-chip communication latency between cores, using thread-level parallelism (TLP) to improve the number of instructions executed per clock cycle, *i.e.*, to improve ILP performance, has shown to be effective for many *general-purpose* applications. However, because of the program characteristics of these applications, effective speculative schemes at both thread- and instruction-level are crucial.

Processors that support speculative multithreading have been proposed for sometime now. However, efforts have only begun recently to develop compilation techniques for this type of processors. Some of these techniques would require efficient architectural support. The jury is still out on how much performance improvement could be achieved for general-purpose applications on this kind of architectures.

In this talk, we focus on a compiler framework that supports thread-level parallelism with the help of control and data speculation for general-purpose applications. This compiler framework has been implemented on the Open64 compiler that includes support for efficient data dependence and alias profiling, loop selection schemes, as well as speculative compiler optimizations and effective recovery code generation schemes to exploit thread-level parallelism in loops and the remaining code regions.

### Power-Efficient Heterogeneous Multicore Technology for Digital Convergence

#### Kunio Uchiyama

Hitachi, Ltd

In recent mobile phones, car navigation systems, digital TVs, and other consumer electronic devices, there is a trend toward digital convergence in which a single device has the ability to process various kinds of applications. At the same time, considering the processing of media content, these devices must be capable of encoding and decoding video images and audio data based on MPEG2, MPEG4, H.264, VC-1, MP3, AAC, WMA, RealAudio, and other formats. Moreover, the latest DVD recorders have the ability to automatically generate digests of video images by using audio and image recognition technology. These kinds of digital convergence devices must be able to flexibly process various kinds of data—media, recognition, data, communications, and so on—and the SoC (System-on-Chip) that is embedded in the devices must deliver superior performance while consuming very small power.

To meet these needs, a power-efficient heterogeneous multi-core technology for the SoC used in consumer electronic devices has been developed. Primary objectives in developing this technology are to: (1) establish a robust heterogeneous multicore architecture that integrates a number of different types of power-efficient processor cores; (2) incorporate dynamic reconfigurable processors to leverage parallelism at the operation level; and (3) create a new software development environment for efficiently developing programs tailored for the heterogeneous multicore architecture. This combination of attributes will give us the superior performance/power ratio and flexibility, while satisfying the enormous demand for digital convergence devices.

The power-thrifty processors used in the heterogeneous multicore architecture essentially include a local memory and an intelligent data transfer unit. Each local memory functions as a distributed shared memory for the entire chip. Processing is speeded up by enabling operations within processors in parallel with data transfers between processors. Dynamic reconfigurable processors called Flexible Engines (FEs) have been implemented as a special type of processor core. The FE executes various arithmetic algorithms fast while dynamically changing the functions and interconnections among 32 arithmetic elements.

A prototype heterogeneous multicore chip has been developed using 90nm technology based on the architecture described above. Four low-power CPU cores are integrated along with two FEs on the 96mm² chip. The CPU core operates at 600 MHz and has a performance of 1.08 GIPS or 4.2 GFLOPS, while the FE operates at 300 MHz, and can perform up to 19.2 GOPS. The chip as a whole delivers a performance of 4.32 GIPS, 16.8 GOPS, and 38.4 GOPS with a power dissipation of less than several watts.

When a program is executed on the heterogeneous multicore chip, the program is divided up into sub-programs, which are processed by the processor cores on the chip

that are best suited to the task based on the attributes of each sub-program part. Multimedia programs such as encoding audio data have been executed on various combinations of CPUs and FEs, and the performance and the power consumption of the various configurations have been evaluated.

A new software development environment has been created for the efficient development of programs specifically tailored for the heterogeneous multicore architecture. Using the new platform, programs are broken up into sub-program parts. The object code for the portions executed by CPU cores is generated using a usual compiler. An FE compiler has been developed for the sub-program parts executed by FEs, and the compiler generates configuration data and sequence control codes tailored for the FEs. A graphical interface editor for optimizing FE libraries has also been developed. It not only enables programmers to write FE programs directly but also enables the programs to be verified by simulation.

A part of the introduced research has been supported by NEDO "Advanced heterogeneous multiprocessor," "Multicore processors for real-time consumer electronics," and "Heterogeneous multi-core technology for information appliances."

## StarDBT: An Efficient Multi-platform Dynamic Binary Translation System

Cheng Wang, Shiliang Hu, Ho-seop Kim, Sreekumar R. Nair, Mauricio Breternitz Jr., Zhiwei Ying, and Youfeng Wu

> Programming Systems Lab, Intel Corporation 2200 Mission College Blvd Santa Clara, CA 95052, USA

{cheng.c.wang,shiliang.hu,ho-seop.kim,sreekumar.r.nair,mauricio.breternitz.jr,victor.ying,youfeng.wu}@intel.com

Abstract. This paper describes the design and implementation of a research dynamic binary translation system, StarDBT, which runs many real-world applications. StarDBT is a multi-platform translation system that is capable of translating application level binaries on either Windows or Linux OSes. A system-level variant of StarDBT can also run on a bare machine by translating the whole system code. We evaluate performance of a user-mode system using both SPEC2000 and some challenging Windows applications. StarDBT runs the SPEC2000 benchmark competitively to other state-of-the-art binary translators. For Windows applications that are typically multi-threaded GUI-based interactive applications with large code footprint, the StarDBT system provides acceptable performance in many cases. However, there are important scenarios in which dynamic translation still incurs significant runtime overhead, raising issues for further research. The major overheads are caused by the translation overhead of large volume of infrequently-executed code and by the emulation overhead for indirect branches.

Keywords: Dynamic binary translation, performance evaluation.

#### 1 Introduction

Dynamic binary translation (DBT) has many attractive applications in computer system designs. For example, it can be used to support legacy binary code [4]; support ISA virtualization [1]; enable innovative co-designed microarchitectures [7], [13], and many others [3], [10], [14], [15], [19], [20]. However, DBT technology also comes with its costs: translation overhead, emulation overhead and potentially other runtime overheads. It is an interesting research topic to obtain insights for designing systems featuring binary translation.

To evaluate DBT design and application, we developed a multi-platform DBT system, named StarDBT. StarDBT translates from IA (Intel Architecture, a.k.a 'x86') to IA, including from IA32 to Intel64. As a multi-platform system, StarDBT can run as a user-mode module that resides in user process space. Currently, we have OS-specific support for user-mode DBT on both Linux and Windows x64 platforms. Furthermore, StarDBT can also serve as a system level DBT that runs directly on

hardware and boots commercial OSes. Abstraction and modularization is the key for StarDBT to support multiple platforms. Specifically, the generic part of the DBT system is separated, modularized and shared. The platform-dependent modules of the DBT are separated from each other and interface with the DBT generic part through an internal API. The DBT system has been stabilized enough to run many real-world applications. Hence, we currently focus on performance evaluation, tuning and obtaining insight on DBT runtime behavior.

For real world deployment, it is important that a new technology handles all kinds of cases and performs well on representative applications. Pathological cases should be identified and handled gracefully. Therefore, we need to evaluate performance on a wide variety of workloads. In this paper, we report our DBT performance for client-side workloads, namely, SPEC2000 and some popular Windows applications.

For the SPEC2000 suite, our StarDBT performs competitively to state-of-the-art DBT systems [4], [5], [17]. Arguably its performance is comparable to native runs (e.g. about 12% performance difference for SPEC2000 on Pentium 4 systems). For Windows applications that are less-benchmarked on most DBT systems, we observed acceptable performance in many cases (e.g. ranging from 10% to 40% slowdowns) and also found interesting performance issues in some others. Performance for Windows applications is critical to our DBT design. On one hand, Windows applications are more representative workloads for most computer users. On the other hand, Windows applications are more challenging for DBT systems -- they are typically multi-threaded, interactive GUI workloads that show different runtime behaviors than the frequently-benchmarked SPEC2000. Our StarDBT system has encountered severe translation overhead for some Windows applications due to their larger code footprint and less code reuse. Meanwhile, more indirect branches (e.g. more function and DLL calls/returns) in Windows workloads also adversely stresses the inefficient indirect branch emulation schemes of software-only DBT systems. In this paper, we strive for better understanding on DBT runtime behavior for Windows workloads and try to gain insights for DBT system design.

This paper describes the StarDBT system, briefing highlights on its design and implementation. Preliminary performance evaluation is also presented. The rest of the paper is organized as follows. Section 2 discusses related work and summarizes the state-of-the-art DBT technology. Section 3 presents the design and implementation of the StarDBT system. Section 4 reports performance evaluation of the system. Section 5 concludes the paper.

#### 2 Related Work

There are a few product systems that adopted the DBT technology [1], [4], [8], [13]. There are also many research papers studying DBT technology [2], [5], [9], [12], [16], [17]. However, DBT runtime overhead has long been a concern for the industry. Performance results are mostly published using hotspot (frequently executed code) dominant workloads such as the SPEC CPU 2000 [11] (referred to as SPEC2000 in this paper). In general, current DBT systems perform from comparably to competitively when compared with native runs for hotspot code. However, non-hotspot (cold, infrequently executed code) performance is less studied.

DynamoRIO [5] is an IA32 to IA32 DBT system that supports flexible binary inspection and instrumentation. Performance numbers are published for the SPEC2000 and four Windows applications. Pin [14] is an instrumentation tool primarily on Linux, with limited Windows support so far. HDTrans [17] is a simple fast Linux-based binary translator. Its simplicity speeds up its cold code translation performance and it shows competitive performance among DBT systems that do not optimize hotspots. Performance is not reported for interactive GUI workloads. FX!32 [6] employs runtime interpretation coupled with off-line static binary translation and optimization. It runs Windows applications, but it does not fit into the DBT category. IA32-EL [4] runs Windows applications on Intel IPF platforms, and published SYSMARK2000 performance results. Although it observed less efficient execution for Windows applications, little is discussed about the underlying dynamics. VMware [1] virtualizes the IA32 instruction set using dynamic binary translation to scan and translate certain resource-sensitive instructions. Therefore, VMware VMMs only translate 3% of the code (OS kernel code) and cause about 4% slowdown due to translation overhead. Transmeta [13] used a code morphing software (CMS) to implement IA32 processors and run IA32 binaries on mobile platforms. However, few performance results are published.

#### 3 StarDBT Design and Implementation

The full spectrum of potential DBT applications motivated our system design to support multiple platforms. The binary translator evaluated in this paper targets translation from IA32 into Intel64 at user level. Namely, it transparently translates 32-bit IA32 application binaries into 64-bit Intel64 code at runtime, enabling full advantages of 64-bit computing for legacy 32-bit applications.

#### 3.1 Multi-platform DBT Architecture

StarDBT runs on both Windows and Linux platforms. StarDBT for Windows platform runs popular Windows desktop applications such as Microsoft Office and Internet Explorer. The Linux version runs command-line Linux applications and also runs on top of a cycle-accurate simulator that simulates at Linux ABI level. Additionally, StarDBT also runs as a system-level virtual machine monitor that boots and runs commercial OSes. StarDBT is designed to boot various commercial OS kernels. At this point, it can boot Linux kernels.

To support such a multi-platform system, we separated the DBT-generic (platform-independent) part from DBT-platform (platform-dependent). The interface between these modules is an internal API named DBT-platform API. DBT-generic requests services such as resource allocation through this API. A DBT-platform module notifies the DBT-generic of certain events such as exceptions or callbacks also through this API.

There are two major components of the DBT system: the binary translator and the runtime system that manages and controls the execution of the entire system. The binary translator components are mostly DBT-generic. However, the runtime system has to be divided into a generic part and a platform (-specific) part. The generic part

of the runtime dispatches execution, and manages the code cache and other important DBT resources in a platform-abstract way. The platform part of the runtime system provides platform-specific services such as initialization, finalization, platform interaction etc. Each platform needs its own specialized implementation of the platform part of the runtime. For example, the Linux platform runtime inserts a kernel module to load the DBT system, which is packed as a Linux user-mode dynamic library. The Windows x64 version DBT-platform runtime rewrites some part of the Microsoft wow64 runtime system to integrate our binary translators.

#### 3.2 Runtime Translation Design

Dynamic binary translation incurs significant runtime overhead; this is especially true for the complex x86 instruction set. Therefore, like most other sophisticated DBT systems, we apply an adaptive translation strategy. It uses a simple fast translator for cold code translation and once a workload hotspot is detected, it applies optimizations.

The simple and fast translation tries to generate target code with minimal runtime overhead. For most IA32 computation instructions (e.g. ALU ops and data moves), the DBT simply decodes and recognizes them. Then the translator copies these instructions to generate Intel64 code. Some IA32 instructions are no longer available in Intel64. These cases are further detailed in Subsection 3.3. Control transfer instructions such as branches, function calls and returns need to be rewritten. This involves some translation lookup and dispatch code (subsection 3.4).

For program hotspots, we form straight-line traces (called regions) to optimize. Because this is conducted at run-time, we only implement a few effective optimizations such as code layout, registerization (for more registers in Intel64) and partial redundancy elimination.

Translators place generated code in code caches for later reuse. The runtime dispatcher maintains a translation lookup table. The execution of the original IA32 code is achieved via emulating in code caches and dispatching in the runtime system. Additionally, we use a 64K-entry translation lookup table as in [5] and we allocate 16MB of memory for code cache. Once the lookup table or the cache is full, we simply flush the code cache.

Generally, it is difficult to maintain true compatibility for user-mode virtual machines due to their memory footprint inside the application process. However, on 64-bit systems, the larger 64-bit memory space offers extra memory space beyond the original 32-bit application space. Thus, our runtime system maintains true compatibility by allocating DBT memory above (outside) the 32-bit user space.

#### 3.3 IA32 to Intel64 Translation

As aforementioned, some IA32 instructions are no longer supported in Intel64. For example, push and pop instructions only support 64-bit operands in 64-bit mode, making it non-straightforward to emulate the 32-bit stack efficiently. In our translator, we generate 64-bit code to emulate 32-bit stack instructions. For example, push32 eax is translated into the following code sequence:

```

lea esp, [rsp - 4]

mov [rsp], eax

```

It is important that the generated code for stack manipulation never uses space beyond its stack pointer, rsp. Some OS kernels may use the space beyond the stack to throw exception and context records for exception handling.

Some IA32 instructions are aliased. However, in Intel64, they have only one opcode available. For example, all eight instructions (as a group) with opcode 82H are the same instructions as those with opcode 80H in IA32. There is a need to remap their opcode to the only opcode available in Intel64: 80H.

There are also IA32 instructions that are missing in Intel64. For example, some BCD arithmetic and bit manipulation operations are no longer supported in Intel64. These instructions can be emulated with a sequence of Intel64 instructions. A tricky part is the segment manipulation instructions in IA32. The 64-mode does not support segmentation directly. Our user-mode StarDBT ignores the segmentation manipulation instructions (except for GS and FS segments which are still supported in Intel64). However, inside the kernel (as seen by our system-mode StarDBT), segmentation are processed in its true architectural sense.

Table 1 summarizes some of our translation from IA32 to Intel64.

Clearly, translating IA32 legacy instructions into Intel64 causes code expansion. The Intel64 REX prefix causes additional code expansion. However, in Intel64, more registers are available and we can exploit these extra registers to improve hotspot code performance.

| Original IA-32 instruction | Translated Intel64 Instruction                             |  |  |  |  |

|----------------------------|------------------------------------------------------------|--|--|--|--|

| PUSH ESP                   | REX. MOV R8/32, ESP                                        |  |  |  |  |

|                            | LEA ESP, [RSP – 4]                                         |  |  |  |  |

|                            | REX. MOV [RSP], R8/32                                      |  |  |  |  |

| PUSH imm/32 (imm/8)        | LEA ESP, [RSP – 4]                                         |  |  |  |  |

|                            | MOV [RSP], imm/32 (imm/32*) // sign extend imm/8 to imm/32 |  |  |  |  |

| PUSH r/32                  | LEA ESP, [RSP – 4]                                         |  |  |  |  |

|                            | MOV [RSP], r/32                                            |  |  |  |  |

| PUSH m/32                  | REX. MOV R8/32, M/32                                       |  |  |  |  |

|                            | LEA ESP, [RSP – 4]                                         |  |  |  |  |

|                            | REX. MOV [RSP], R8/32                                      |  |  |  |  |

| POP ESP                    | MOV ESP, [RSP]                                             |  |  |  |  |

| POP r/32                   | MOV r/32, [RSP]                                            |  |  |  |  |

|                            | LEA ESP, [RSP + 4]                                         |  |  |  |  |

| POP m/32                   | REX. MOV R8/32, [RSP]                                      |  |  |  |  |

|                            | REX. MOV m/32, R8/32                                       |  |  |  |  |

|                            | LEA ESP, [RSP + 4]                                         |  |  |  |  |

| ENTER imm16, imm8          | LEA ESP, [RSP – 4]                                         |  |  |  |  |

|                            | MOV [RSP], EBP                                             |  |  |  |  |

|                            | LEA ESP, $[RSP - imm16]$ $(imm16 > 0)$                     |  |  |  |  |

|                            | REX. MOV R8/32, [EBP – 4]                                  |  |  |  |  |

|                            | REX. MOV [RSP + imm16 – 4], R8/32                          |  |  |  |  |

|                            |                                                            |  |  |  |  |

|                            | REX. MOV R8/32, [EBP – 4 * imm8 + 4] (imm8 > 1)            |  |  |  |  |

|                            | REX. MOV [RSP + imm16 – $4 * imm8 + 4$ ], R8/32 (imm8 > 1) |  |  |  |  |

|                            | LEA EBP, [RSP + imm16]                                     |  |  |  |  |

|                            | MOV [RSP + imm16 – $4 * imm8$ ], EBP (imm8 > 0)            |  |  |  |  |

| LEAVE                      | MOV ESP, EBP                                               |  |  |  |  |

|                            | MOV EBP, [RSP]                                             |  |  |  |  |

|                            | LEA ESP. [RSP + 4]                                         |  |  |  |  |

**Table 1.** Translation of Some IA32 Instructions

#### 3.4 Control Transfers in Code Cache

Control transfers between translated code in the code cache can cause significant runtime overhead if handled inefficiently, because of the need to look up translated addresses. StarDBT eliminates direct jumps and (eventually) chains direct conditional branches together, maintaining execution in the code cache. Indirect branches are inlined with dispatch code to lookup the translation mapping table for their translated targets. The translation mapping table for large footprint applications can be quite big. We speed up this dispatch code for indirect branch target lookup with a special cache table. Return instructions are handled similarly to indirect branches.

#### 4 Evaluation and Characterization

#### 4.1 Evaluation Methodology

We evaluate our StarDBT system using both SPEC2000 and widely-used Windows GUI-based interactive applications (mostly from the SYSMARK 2004 SE [18]). We run SPEC2000 as a whole to collect the baseline performance numbers. These data can be compared with prior DBT systems and they are good performance indicators for batch-mode and long-run applications. We selected seven Windows applications to study DBT performance for interactive workloads. Unfortunately, the SYSMARK 2004 SE benchmark is too large (and out of our script control) for performance characterization tools. Therefore, we developed our own automation scripts to run these applications. Whenever possible, we develop scripts that run similar scenarios as the original SYSMARK 2004. Otherwise, we develop scenarios that reflect common usage of the benchmarked software. The workload scenarios will be described shortly.

We use the Intel VTune Performance Analyzer v8.02 to study performance issues. In our experiments, we emphasize the measurement of response time for interactive workloads. In many cases, this can be measured by a timer. However, this is more or less subjective and imprecise. For example, sometimes the GUI response looks ready for user's interaction; however some background processing may be still active. A timer measurement in this situation is not well-defined. In our study, we use the number of duty cycles (collected by VTune) to measure the response time. The duty cycle in VTune is defined as the number of cycles that processors use to execute instructions from the application(s) being monitored.

We use two generations of machines to study platform sensitivity in our study. The first machine is a 3.60GHz (Pentium 4) Xeon based dual-processor system that runs Windows 2003 x64 server. It has 1MB L2 cache per core and 2GB memory. The second machine is a 3.0GHz Intel Xeon 5160 (Woodcrest) based Dell Precision 490 workstation, also running Windows 2003 x64 server. The Dell Woodcrest system has two dual-core Woodcrest processors (4 processor cores) and 4GB of memory.

#### 4.2 Windows Interactive Workloads

The criteria for developing our workloads are: (1) The scenarios must be representative of user interactive applications, using widely-used software; (2) the

benchmark scripts should run long enough to be realistic, but short enough to be characterized (using VTune). We use the same BAPCO SYSMARK 2004 scenarios whenever possible. And eventually we developed the following workload scenarios in the test: (Non-Microsoft software in SYSMARK 2004 could not be launched outside the SYSMARK scripts)

- Access: the script opens the SYSMARK 2004 sales database, performs two queries and then exports the result to Excel format.

- *Excel*: the script opens the worksheets from the SYSMARK 2004. It performs two sorting operations and calculates values for large columns based on formulas. Finally, it does some auto formatting.

- **Power Point (PPT):** this script opens the car sales and commercial presentation from SYSMARK 2004. Then it shows slides of the 70-second presentation that contains figures, animations and a short video clip.

- *Word*: this script opens the Tom Sawyer document from the SYSMARK 2004. It performs a set of formatting, editing operations before a final print-preview.

- Internet Explorer (IE): this script activates the IE browser, searches on Google for SYSMARK 2004 and its white paper. It opens the white paper, flips through and closes it. Then it surfs several well-known websites such as CNN and ESPN. It also searches OLE automation documents from MSDN and finally it checks our local weather from weather.com and a stock page from Google Finance.

- *Media Player (MPlayer)*: this script loads and plays the SYSMARK 2004 car commercial video clip (68 seconds).

- Visual Studio (VStudio): this is our own benchmark scenario. It opens Microsoft Platform SDK and builds our entire StarDBT system. In a sense, it is similar to self compilation tests for many compilation systems.

Table 2 shows some basic characteristics of our benchmark scenarios when they run natively on the Dell 490 Woodcrest system without DBT. The first data column shows the instruction count for each benchmark run. The second data column shows the duty cycles for each run, collected by VTune. And the third data column shows the elapsed wall time for the benchmark scenario, including user thinking time. It is clear that most benchmarks run tens of seconds and tens of billions duty cycles.

| BENCH MARK | INSTR COUNT<br>(BILLIONS) | DUTY CYCLE<br>(BILLIONS) | WALL TIME<br>(SECOND) |

|------------|---------------------------|--------------------------|-----------------------|

| Access     | 65.607                    | 52.281                   | 76                    |

| Excel      | 8.178                     | 11.038                   | 69                    |

| PPT        | 123.117                   | 159.169                  | 77                    |

| Word       | 6.765                     | 11.253                   | 69                    |

| IE         | 15.369                    | 25.501                   | 83                    |

| MPlayer    | 43.113                    | 44.463                   | 70                    |

| VStudio    | 48.576                    | 69.114                   | 43                    |

Table 2. Benchmark basic characteristics

#### 4.3 SPEC2000 Performance

Although we have developed hotspot optimizations in our StarDBT system, they are not particularly helpful in our GUI interactive scenarios and sometime degrade performance. Furthermore, to compare with prior projects, it is important to have a consistent setting. Therefore, in our baseline performance measurement using SPEC2000, we disabled hotspot optimizations except hot trace re-layout.

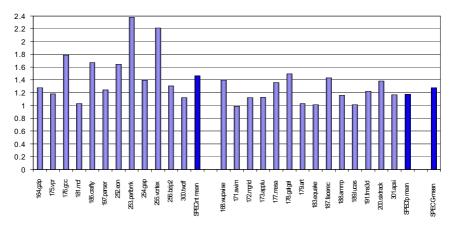

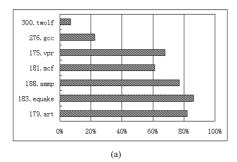

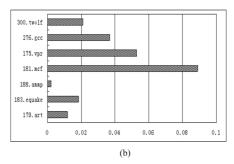

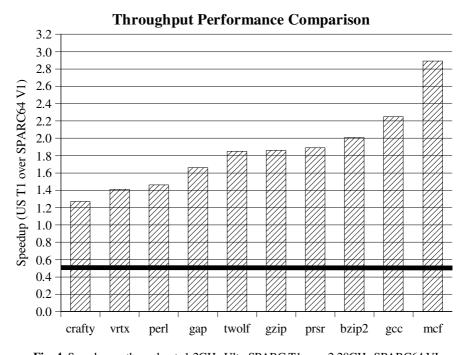

Given the StarDBT settings above, Figure 1 shows the SPEC2000 performance running on our StarDBT system on the Woodcrest system. The input binaries are compiled with Intel ICC compiler 9.0 at the highest optimization level (O3) with profile feedback. Because hotspot optimizations are not invoked, StarDBT's slow-downs are due to DBT translation and emulation overhead. The average slowdown for

(a) SPEC2000 Performance on Woodcrest platform

(b) SPEC2000 performance on Pentium 4 platform

Fig. 1. SPEC2000 performance

integer benchmarks is about 46% while the FP benchmarks show an average slowdown of 17%, making the aggregate slowdown for the entire SPEC2000 approximately 27%. However, the same performance test on the Pentium 4 machine shows respectively 25%, 2% and 12% slowdowns for the SPEC2000 integer, FP and entire suite. The performance difference between the two generations of processors reflects the different processor efficiency and the memory hierarchy efficiency of the test platforms. The new Woodcrest processors are more efficient and thus are more sensitive to extra instructions caused by DBT dynamic instruction count expansion. This effect can be seen even from the same platform while running applications with different memory behavior. For example, in Figure 1, memory intensive (thus pipeline less efficient) programs such as mcf and FP benchmarks cause less slowdown than CPU intensive programs on both platforms.

DynamoRIO [5] reported slightly better performance (17% slowdown for SPEC2000 integer, with a different experimental setting) than our StarDBT when only simple translation is enabled. HDTrans [17] also translates from IA32 to IA32 and reported slightly better performance than DynamoRIO. Although the quality of the input binaries and the experimental machines may influence the performance differences, all these experiments demonstrate that current DBT systems can work fairly well on CPU intensive workloads where program footprint is small and the translated code is heavily reused.

#### 4.4 Interactive Application Performance

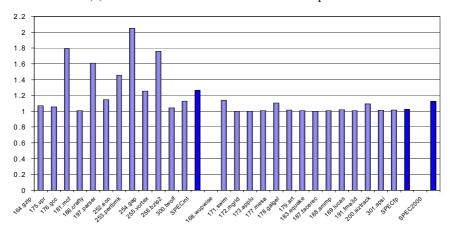

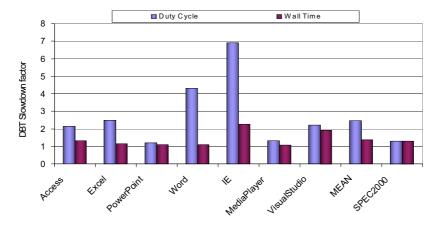

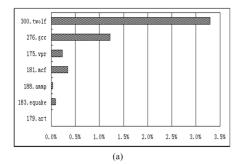

To better understand how DBT affects user experience of Windows applications, we collect responsiveness data when running Windows applications on top of our StarDBT. The responsiveness is measured both by timing elapsed wall clock time and by collecting the duty cycle numbers using VTune. Figure 2 graphs the slowdown factor (when compared with native runs on Woodcrest) of the scenarios described in subsection 4.2.

Fig. 2. Window application responsiveness slowdown

It is found that the responsiveness in terms of wall time is not too bad, 35% slowdown on average, slightly worse than the SPEC2000 slowdown. In our actual user experience, there is little noticeable difference between DBT runs and native runs for four out of the seven scenarios (MPlayer, PPT, Excel and Word). However, there are cases, like the IE scenario, which are much slower and users clearly experience the slowdown while loading web pages. On the other hand, the responsiveness measured by duty cycles is worse than what the wall time slowdown suggests. On average, DBT runs are executing 2.4 times more duty cycles than native runs. For reference, the SPEC2000 DBT runs show the same duty-cycle expansion factor as the slowdown factor. The significantly more duty cycles for interactive workloads have both performance and power efficiency implications.

Specifically for each individual benchmark, we observed different runtime behavior. For example, PPT and MPlayer scenarios render real time presentations at certain pace. Their duty cycle expansion can hardly be noticed by users. Rather, it appears as slightly heavier CPU utilization. Excel and Word scenarios are more interactive. They exercise many different features of the tested software for editing or formatting. However, on today's processors, the extra duty cycles they caused are a relatively short period of real time for end-user experience. The Visual Studio scenario is an interesting case. It invokes Microsoft C/C++ compiler many times to compile the files in our StarDBT project. Each file is compiled by a separate compiler process. Since the StarDBT is a user-mode module inside each process, cross-process translation sharing is not supported. Thus our DBT caused many repeated retranslations during the entire project build. Since the DBT build is more like a batch job, the more duty cycles clearly show as wall time slowdown. Although user-mode DBT causes serious overhead for such cases, it should be in a much better position when translation is done at system level, where translation is managed at the physical memory level. The worst user experience in our benchmarks is IE surfing. In a sense IE is a software framework that loads many other software modules to process different web document sections. This is especially true for today's webpage designs. Many webpages involve dynamic scripting and plug-in technology that invokes JVM, flash player, PDF readers, and many other document/content process modules. Consequently IE causes the worst slowdown (7X) in terms of duty cycles and more than 2X in terms of wall clock time.

#### 5 Conclusion

Binary translation has many potential applications and it enables new features to computer systems cost-effectively. However, its runtime overhead has long been a concern. Many recent DBT systems have been fairly successful in running CPU intensive workloads. However, performance characterization has not been clear for GUI-based interactive Windows applications.

We have developed a state-of-the-art dynamic binary translation system, StarDBT, which runs on multiple platforms. The user-mode StarDBT demonstrates comparable performance to other cutting-edge runtime translation systems [4], [5], [16], [17] when running the SPEC2000 benchmarks. Additionally, we study performance using popular Windows applications.

In general, we found that current software binary translation technology can provide acceptable responsiveness in many cases. However, clear slowdowns are still experienced for some common user applications. In our evaluation, we collected and analyzed detailed performance data to achieve insight into this subject. We found that dynamic instruction count expansion is the primary performance factor for the DBT runs. This expansion is due to (1) emulation overhead for unsupported instructions and control transfers (for steady state performance in code cache) and (2) translation overhead for big footprint workloads and interactive workloads. We are using the insight from this performance characterization to guide future research that will address these performance issues.

#### Acknowledgements

We would like to thank Jesse Fang for his strong support of the StarDBT project. We would also like to thank our colleagues at Programming Systems Lab for their contributions to the StarDBT infrastructure.

#### References

- Adams, K., Agesen, O.: A Comparison of Software and Hardware Techniques for Virtualization. In: 8th Int'l Symp. on Architecture Support for Programming Languages and Operating System, pp. 2–13 (2006)

- Altman, E.R., Gschwind, M., Sathaye, S., Kosonocky, S., Bright, A., Fritts, J., Ledak, P., Appenzeller, D., Agricola, C., Filan, Z.: BOA: the Architecture of a Binary Translation Processor. IBM Research Report RC 21665 (2000)

- 3. Bala, V., Duesterwald, E., Banerjia, S.: Dynamo: A Transparent Runtime Optimization System. In: ACM SIGPLAN Conf. on Programming Language Design and Implementation, pp. 1–12 (2000)

- Baraz, L., Devor, T., Etzion, O., Goldenberg, S., Skalesky, A., Wang, Y., Zemach, Y.: IA-32 Execution Layer: A Two Phase Dynamic Translator Designed to Support IA-32 Applications on Itanium®-based Systems. In: 36th Int'l Symp. on Microarchitecture, pp. 191–202 (2003)

- 5. Breuning, D.L.: Efficient, Transparent, and Comprehensive Runtime Code Manipulation. Ph.D thesis, Massachusetts Institute of Technology (2004)

- Chernoff, A., Hookway, R.: DIGITAL FX!32 Running 32-Bit x86 Applications on Alpha NT. In: USENIX (1997)

- 7. Cmelik, R.F., Ditzel, D.R., Kelly, E.J, Hunter, C.B., et al.: Combining Hardware and Software to Provide an Improved Microprocessor, US Patent 6,031,992 (2000)

- 8. Dehnert, J.C., Grant, B., Banning, J., Johnson, R., Kistler, T., Klaiber, A., Mattson, J.: The Transmeta Code Morphing Software: Using Speculation, Recovery, and Adaptive Retranslation to Address Real-Life Challenges. In: 1st Int'l Symp. on Code Generation and Optimizations, pp. 15–24 (2003)

- Ebcioglu, K., Altman, E.R.: DAISY: Dynamic Compilation for 100% Architectural Compatibility. In: IBM Research Report RC 20538 (1996) Also: 24th Int'l Symp. on Computer Architecture (1997)

- Edson, B., Wang, C., Wu, Y., Araujo, G.: Software-Based Transparent and Comprehensive Control-Flow Error Detection. In: 4th Int'l Symp. on Code Generation and Optimizations, pp.333–345 (2006)

- 11. Henning, J.L.: SPEC CPU 2000: Measuring CPU Performance in the New Millennium. IEEE Computer 33(7), 28–35 (2000)

- 12. Horspool, R.N., Marovac, N.: An Approach to the Problem of Detranslation of Computer Programs. Computer Journal (August 1980)

- 13. Klaiber, A.: The Technology Behind Crusoe Processors, Transmeta Technical Brief (2000)

- Luk, C., Cohn, R., Cohn, R., Muth, R., Patil, H., Klauser, A., Lowney, G., Wallace, S., Reddi, V., Hazelwood, K.: Pin: Building Customized Program Analysis Tools with Dynamic Instrumentation. In: ACM SIGPLAN Conf. on Programming Language Design and Implementation, pp. 190–200 (2005)

- 15. Qin, F., Wang, C., Li, Z., Kim, H.-S., Zhou, Y., Wu, Y.: LIFT: A Low-Overhead Practical Information Flow Tracking System for Detecting Security Attacks. In: 39th Int'l Symp. on Microarchitecture, pp. 135–148 (2006)

- Scott, K., Kumar, N., Velusamy, S., Childers, B., Davidson, J., Soffa, M.: Retargetable and Reconfigurable Software Dynamic Translation. In: 1st Int'l Symp. on Code Generation and Optimizations, pp. 36–17 (2003)

- 17. Sridhar, S., Shapiro, J.S., Northup, E., Bungale, P.: HDTrams: An Open Source, Low-Level Dynamic Instrumentation System. In: 2nd Int'l Conf. on Virtual Execution Environments, pp. 175–185 (2006)

- 18. SYSMARK 2004, Second Edition, http://www.bapco.com/products/sysmark2004/

- Wu, Q., Reddi, V., Wu, Y., Lee, J., Conners, D., Brooks, D., Martonosi, M., Clark,

D.:Dynamic Compilation Framework for Controlling Microprocessor Energy and

Performance. In: 38th Int'l Symp. on Microarchitecture, pp. 271–282 (2005)

- Ying, V., Wang, C., Wu, Y., Jiang, X.: Dynamic Binary Translation and Optimization of Legacy Library Code in a STM Compilation Environment, WBIA06 in conjunction with ASPLOS (2006)

#### **Unbiased Branches: An Open Problem**

Arpad Gellert<sup>1</sup>, Adrian Florea<sup>1</sup>, Maria Vintan<sup>1</sup>, Colin Egan<sup>2</sup>, and Lucian Vintan<sup>1</sup>

<sup>1</sup> Computer Science Department, "Lucian Blaga" University of Sibiu, Emil Cioran Street, No. 4, 550025 Sibiu, Romania {arpad.gellert,adrian.florea,lucian.vintan}@ulbsibiu.ro

<sup>2</sup> School of Computer Science, University of Hertfordshire, Hatfield, College Lane, AL10 9AB UK

c.egan@herts.ac.uk

**Abstract.** The majority of currently available dynamic branch predictors base their prediction accuracy on the previous k branch outcomes. Such predictors sustain high prediction accuracy but they do not consider the impact of unbiased branches, which are difficult-to-predict. In this paper, we evaluate the impact of unbiased branches in terms of prediction accuracy on a range of branch difference predictors using prediction by partial matching, multiple Markov prediction and neural-based prediction. Since our focus is on the impact that unbiased branches have on processor performance, timing issues and hardware costs are out of scope of this investigation. Our simulation results, with the SPEC2000 integer benchmark suite, are interesting even though they show that unbiased branches still restrict the ceiling of branch prediction and therefore accurately predicting unbiased branches remains an open problem.

**Keywords:** Branch prediction, unbiased branch, branch difference value prediction.

#### 1 Introduction

In a previous paper [1] we showed that a branch in a certain dynamic context is difficult-to-predict when that branch is unbiased and its outcomes are nondeterministically shuffled. A branch is unbiased if its behaviour does not demonstrate a tendency to either the taken or the not taken path. We quantified and demonstrated that the percentages of difficult-to-predict branches in the SPECcpu2000 benchmarks suite [2] are significant (averaging between 6% and 24%, depending on the type of branch prediction context and the prediction context length). We considered the ceiling of history context-based prediction to be around 94% if the feature set length of 28 bits is used. Furthermore, we showed that many current state-of-the-art conventional branch predictors are unable to accurately predict these unbiased branches. This is because current branch predictors only use a limited amount of prediction information, such as local- or/and global-correlations and path-based information. The use of such limited information means that unbiased branches cannot be predicted to a high degree of accuracy. Consequently, other information is required to predict branches which have been classified as unbiased. In this paper we investigate the use of a branch condition sign. The condition sign can be either positive, negative or zero. The condition sign is the difference between the data operands held within each source register. For example, a positive condition sign is computed if the datum in the first source register is greater than the datum in the second source register, and vice-versa for a negative condition sign, and zero if the data show equality. We show that branch behaviour is predictable by predicting the condition sign because branch's output is deterministically correlated with the condition's sign, but the impact of unbiased branches remains significantly high.

#### 2 Related Work

Smith [3] showed that the majority of mispredicted branches come from few static branches. He also showed that a context-predictor where the last 'n' (as low as 2) data values produced or consumed are used in combination with a closing outer-loop counter can achieve better prediction accuracy than a conventional *gshare* predictor.

Heil [4] introduced the idea of a Branch Difference Predictor (BDP) which simply holds branch source register differences. Heil used these data-value differences as inputs into a Rare Event Predictor (REP). The Rare Event Predictor was used to predict difficult-to-predict branches and the majority of easy-to-predict branches were predicted with a conventional *gshare* predictor. In Heil's study a difficult-to-predict branch was a branch that was mispredicted by a conventional *gshare* predictor. In contrast to Heil, we define in [1] a difficult-to-predict branch to be a branch with a low degree of polarisation since that tends to shuffle between taken and not-taken and is therefore unbiased. Heil used the differences in the register data values as inputs to the REP (up to a maximum of 3 value differences), whereas in our study we use the sign of the differences (up to a history of 256 sign differences) between the register data values. We therefore use less storage and our simulation results show that we achieve better prediction accuracy.

In [5], González introduced the concept of branch prediction through value prediction (BPVP). The idea was to pre-compute a branch outcome by speculatively predicting the source operand as each branch is dynamically encountered. González's prediction strategy was to use a conventional *gshare* in conjunction with a BPVP. The inclusion of the BPVP was to predict the branches that were difficult-to-predict by the conventional *gshare* predictor. González therefore has a similar approach to Heil.

Vintan [6] proposed pre-computing branches by determining a branch outcome as soon that branch's operands were available. The basis behind such pre-computation was that the instruction that produced the last branch source operand would also trigger the branch condition estimation. This means that as soon as this operation was completed then the branch outcome could be immediately resolved. Even though this concept would provide (almost) perfect prediction accuracy, there was a heavy timing penalty in the case when a branch instruction is dynamically executed immediately after the last source operand has been computed, in fact this is a common case.

Gao [7] implemented a Prediction by Partial Matching (PPM) predictor that predicts branch outcomes by combining multiple partial matches through an adder tree. The Prediction by combining Multiple Partial Matches (PMPM) algorithm selects up to L confident longest matches and sums the corresponding counters that are used to furnish a prediction. A bimodal predictor is used to predict branches that are completely biased

(either always taken or always not taken) and the PMPM predictor is used to furnish a prediction when a branch is not completely biased. In this study we also implement a PPM predictor, but our PPM predictor has three significant differences. First, our Branch Difference Prediction by Combining Multiple Partial Matches (BPCMP) furnishes predictions for unbiased branches identified in our previous work [1, 8] instead of not completely biased branches. Second, in Gao's study global branch history information was used, whereas we use a combination of global and local branch difference history information. Finally, Gao used an adder tree algorithm to combine multiple Markov predictions, we use one of two voting algorithms.

Jiménez [9] proposed a neural predictor that uses fast single-layer perceptrons. In his first perceptron-based predictor the branch address is hashed to select the perceptron, which is then used to furnish a prediction based on global branch history. Jiménez [10] furthered his work by developing a perceptron-based predictor that uses both local and global branch history information. We also evaluate a perceptron-based predictor, but unlike Jiménez our inputs are based on global and local branch operand difference information. In [11] Jiménez developed a piecewise linear predictor using a piecewise linear function the idea being to exploit different paths leading to the branch undergoing prediction. We have also evaluated a piecewise linear predictor on the unbiased branches as described in [12].

#### 3 Unbiased Branches

In [1] we define an unbiased branch to be a branch that does not demonstrate a bias to either the taken or the not taken path which means unbiased branches show a low degree of polarisation towards a specific prediction context (by which we mean, a local prediction context or a global prediction context or a path-based prediction context) and are therefore difficult-to-predict by that particular prediction context.

We also identified branches that were unbiased on their local and global history contexts and, on their global history XORed with the branch address. Our results showed that even with a feature set length of 28 bits the number of unbiased branches remained significantly high at just over 6%. We therefore considered the ceiling of history context-based prediction to be around 94%.

#### 3.1 Condition-History-Based Branch Prediction Using Markov Models

A context-based predictor [13] predicts the next datum value based on a particular stored pattern that is repetitively generated in the values' sequence. This means that, a context-based predictor could predict any stochastic repetitive sequence. Value predictors that implement the PPM algorithm represent an important class of context-based predictors. In a PPM predictor, if a prediction cannot be furnished by order k then the pattern length is shortened and the Markov predictor of order k-l is used to furnish the prediction and if this order cannot furnish a prediction the order is further reduced to k-l and so on until either a prediction is furnished or the Markov predictor is of the order l.

#### 3.1.1 Local Branch Difference Predictor

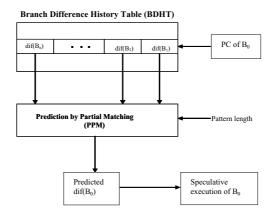

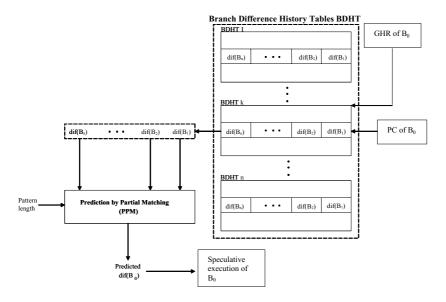

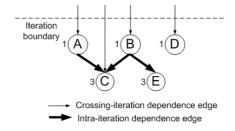

In Figure 1 we show the mechanism of our local PPM Branch Difference Predictor. The Branch Difference History Table (BDHT) is indexed by the branch address ( $B_0$ ). In

the case of a hit in the BDHT, the last h dynamic source operand differences are furnished. To save storage space, sign operand differences are recorded as +1, -1 or 0. For each dynamic branch encountered, a positive difference is recorded if the first source operand is greater than the second, a negative difference is recorded if the first source operand is less than the second source operand and zero is recorded if both operands are the same. The h difference fields of the BDHT entry are then used as inputs into our complete-PPM predictor. The PPM predictor furnishes the predicted sign value of the branch undergoing execution ( $B_0$ ) of order k, where k < h. Speculative execution of the branch ( $B_0$ ) only occurs in the case that the pattern length k is repeated in the last h differences with a frequency greater than or equal to a threshold value.

Fig. 1. A local complete-PPM branch-difference predictor

Fig. 2. A global and local complete-PPM branch-difference predictor

#### 3.1.2 Combined Global and Local Branch Difference Predictor

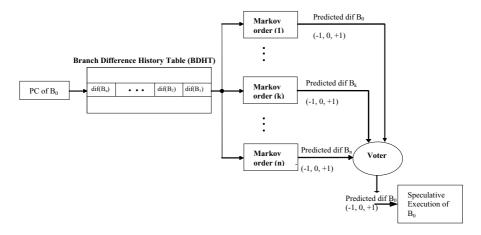

Figure 2 shows the branch prediction mechanism using a combined global and local PPM-based branch-difference predictor. The Global History Register (GHR) contains the global branch difference history pattern. Every global branch history pattern has its own BDHT and the GHR history pattern is used as an index to its BDHT. Each BDHT is configured as a local BDHT and is accessed as described in section 3.1.1.

#### 3.1.3 Branch Difference Prediction by Combining Multiple Partial Matches

Figure 3 shows our branch prediction mechanism using the Branch Difference Prediction by Combining Multiple Partial Matches (BPCMP). An entry in the BDHT is accessed by the method described in section 3.1.1, but now the h branch differences are used as inputs into multiple Markov predictors of different orders (n where n < h). Each Markov predictor furnishes a predicted sign value (+1, -1 or 0) and these multiple predictions are passed to a voter. The final value prediction is then furnished as the greatest sign frequency that was input into the voter.

Fig. 3. Multiple Markov branch-difference prediction

We have also investigated a confidence-based voting mechanism. The function field of each entry in the BDHT holds n saturated confidence counters, in the range -4 to +4, which are associated with the n Markov predictors. For a pattern length k, where  $1 \le k \le n$ , the Markov predictors will furnish a value prediction if that repeating pattern is stored at least once in its h history values. In the case of a correctly predicted branch, its confidence saturating counter is incremented and decremented in the case of a misprediction. The Markov prediction is then replicated to match its confidence counter, so long as that confidence counter is >0. These multiple value predictions are then passed to the voter, which furnishes the most frequent value prediction.

#### 4 Simulations

We have developed a number of simulators (as described in section 3) which extend the sim-bpred simulator provided in SimpleSim-3.0 [14]. We also include implementations

to identify unbiased branches as presented in [1, 8]. We have evaluated our simulators using the unbiased branches we identified in [1] on the SPEC2000 benchmark suite [2]. All simulation results are reported on 1 billion dynamic instructions skipping the first 300 million instructions. We emphasise that our investigation is about the identification and the impact that unbiased branches have on dynamic branch prediction and therefore realistic hardware costs and timings are out of scope of this investigation.

#### 4.1 Local Branch Difference Prediction

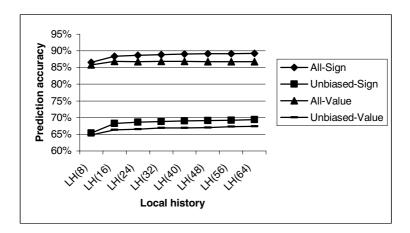

We set out to determine the optimal local branch difference predictor. We asked ourselves 5 questions. Would the operand sign value difference algorithm achieve better prediction accuracy than the operand value difference? Which local history register length would provide the best prediction accuracy? Which pattern length would achieve the best prediction accuracy? What is the most suitable threshold value? What is the ideal number of local BDHT entries?

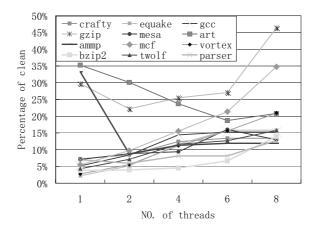

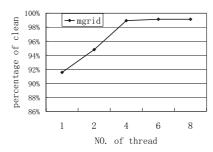

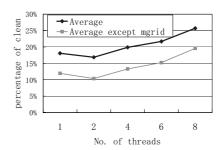

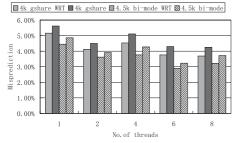

In Figure 4 we answer the first two questions: What would be the most suitable sign algorithm to use and, which history register length achieves the best prediction accuracy? We identified unbiased branches the same way as in our previous work [1], and we evaluated the impact of these unbiased branches using a complete PPM predictor with a local BDHT. The BDHT we used was sufficiently large to ensure that every static branch had its own entry thereby eliminating any possibility of collisions. The pattern length was set to 3, the threshold value was set to 1, and the local history register length was varied from 8-signs to 64-signs in increments of 8. Our results show that better prediction accuracy is achieved by the operand sign difference algorithm rather than the operand value difference algorithm and that beyond a local history register length of 24-signs there is only marginal improvement in prediction accuracy. The reason that the operand sign difference algorithm outperforms the operand value difference algorithm is due to the increased amount of correlation information used by the sign difference algorithm. The frequency of information used

**Fig. 4.** Average difference prediction accuracy with increasing local history register length of the sign difference and operand difference algorithms

by the operand value difference algorithm is low and therefore correlation is low, whereas the frequency of information used by the operand sign difference algorithm is high and therefore correlation is high.

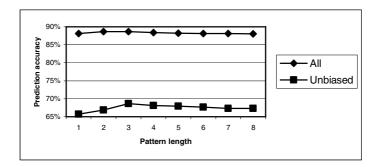

In Figure 5 we answer the third question: Which pattern length would achieve the best prediction accuracy? We used a complete PPM predictor with the operand sign

Fig. 5. Average difference prediction accuracy with increasing pattern length

Fig. 6. Average difference prediction accuracy with increasing threshold value

Fig. 7. Average difference prediction accuracy with an increase in the number of local BDHT entries

difference algorithm, a local history register length of 24-signs and the threshold value was set to 1. Our results show that initially prediction accuracy improves with increasing pattern length and then decreases and these results confirm that our original pattern length of 3 achieves the best prediction accuracy.

In Figure 6 we answer the fourth question: What is the most suitable threshold value? We used the same parameters as Figure 5, but the pattern length was now set to 3 and the threshold value varied. Our results show that prediction accuracy improves with an increasing threshold value, but there is marginal, if any, benefit of increasing the threshold value beyond 7.

In Figure 7 we answer the final question: What would be the optimal number of entries in the local BDHT? We used the same parameters as Figure 6, and the number of entries in the local BDHT was varied from 64 entries to 256 entries in increments of 64. We also include an unlimited local BDHT. Our results show that the impact of the so called 3Cs (capacity, collisions and cold-start) to be minimal with a 256 entry local BDHT and that there is minimal prediction accuracy gain by increasing the number of entries beyond 256 entries where the increased number of cold-start mispredictions may impact on prediction accuracy.

We investigated the branch prediction accuracies of the individual SPEC2000 benchmarks using our optimal local branch difference predictor. We used the operand sign difference algorithm, with a local history register length of 24-signs, a pattern length of 3, and we use a local 256 entry BDHT. In our results we compare two threshold values, 1 and 7. When the threshold value is 1, we achieve an average branch prediction accuracy of 90.55% and the unbiased branches have an average branch prediction accuracy of 71.76%. When the threshold value is increased to 7, we achieve an average branch prediction accuracy of 96.43% and the unbiased branches have a prediction accuracy of 76.69%. These results show the significance of the threshold value on prediction accuracy and the impact of unbiased branches. Consequently, unbiased branches in this local context remain difficult-to-predict.

#### 4.2 Combined Global and Local Branch Difference Prediction

We consider the high number of unbiased branches and their impact on prediction accuracy to be due to their high degree of shuffling. To alleviate the problem of shuffled branch behaviour of unbiased branches we have developed a combined global and local branch difference predictor which would convert an unbiased branch in a local context into a biased branch in a global context, and therefore a difficult-to-predict branch in a local context would be an easy-to-predict branch in a global context.

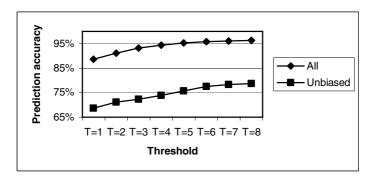

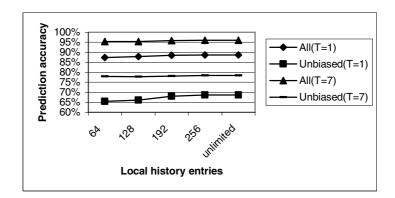

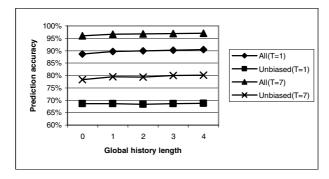

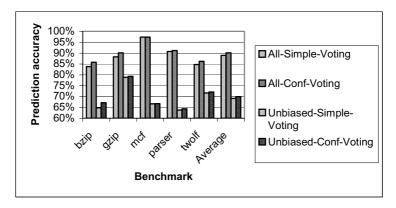

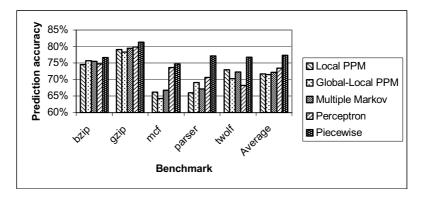

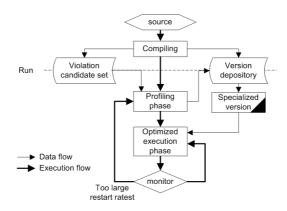

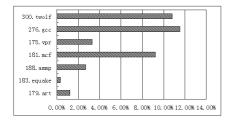

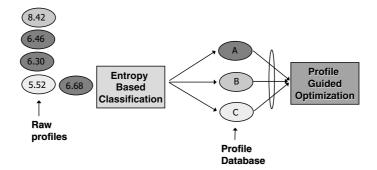

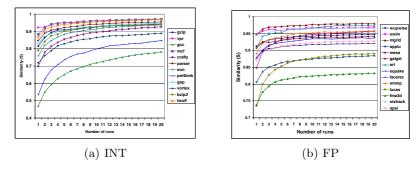

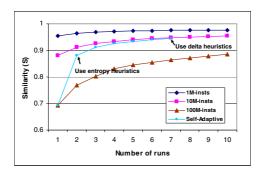

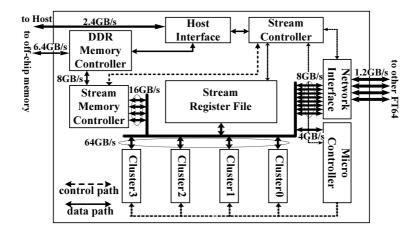

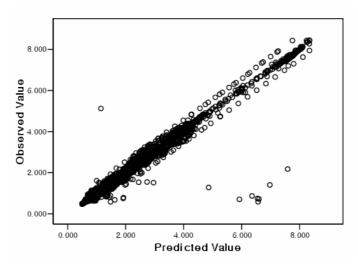

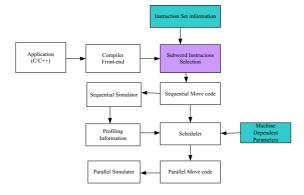

In our global and local branch difference predictor, each global history register pattern is used to point to its own local BDHT as described in section 3.1.2 and shown in Figure 2. Consequently, we restrict the global history register length to a maximum of 4-signs. The parameters of each of the local BDHTs were the same as those which achieved the results shown in Figure 7, except we used a 256 entry BDHT.